Architecture des ordinateurs

les circuits asynchrones

De la représentation des données à l'électronique

On a vu que toutes les données étaient numériques dans un ordinateur, et finalement représentées par des suites de 0 et de 1. Cela vient en partie du succès de l'électronique numérique, surtout depuis l'invention des transistors. La valeur logique 1 est représentée par un potentiel électrique « haut », par exemple 2 volts, et la valeur logique 0 par un potentiel « bas », par exemple 0 volt. Selon la technologie utilisée, la différence entre les deux potentiels pourra être plus grande ou moins grande.

Assemblage de transistors

Un processeur contient un certains nombre de circuits capables de réaliser des calculs en binaire : addition, soustraction, ... ou certaines manipulations sur des données (des décalages par exemple). Nous allons voir dans ce chapitre comment de tels circuits peuvent être réalisés par des assemblages de transistors.

Microélectronique ou informatique

Ce chapitre est à la croisée des chemins entre deux matières : la microélectronique et l'informatique, qui étudient toutes deux le fonctionnement du transistor. Nous garderons toutefois le point de vue de l'informaticien qui ne va s'intéresser qu'au comportement logique du transistor. Nous ne nous intéresserons pas à la consommation des transistors, à la réalisation pratique de ces transistors sous forme de masque, à leur effet capacitif, à l'évacuation de la chaleur, ...

Les transistors MOS

A la base des processeurs modernes, il y a le transistor MOS : un processeur n'est rien d'autre qu'un assemblage de transistors connectés par des conducteurs ! On peut réunir sur un processeur de moins de un centimètre carré des centaines de millions de transistors. Il existe deux types de transistor MOS : le transistor N et le transistor P qui ont des comportements complémentaires.

Remarque : La technologie MOS peut utiliser des potentiels hauts très variables. Nous choisirons ici une technologie de 2 volts.

- Transistor N

Le transistor NMOS (type N) est un circuit électronique ayant 3 points importants : la source notée S, le drain noté D et la grille notée G. Le comportement de ce circuit est le suivant : si la grille est reliée à un potentiel de 0 volt, alors la source et le drain seront électriquement isolés, on dit que le transistor est bloqué. Si la grille est reliée à un potentiel haut (2 volts) par exemple) il y aura conduction entre la source et le drain, on dit que le transistor est passant. Schématiquement il s'agit donc d'un interrupteur commandé par un signal électrique. Une contrainte supplémentaire propre à la technologie MOS est que le transistor de type N fait bien passer le 0 (depuis la source vers le drain), mais assez mal le 1.

- Transistor P

Le transistor PMOS (type P) est un circuit électronique ayant 3 points importants : la source notée S, le drain noté D et la grille notée G. Le comportement de ce circuit est le suivant : si la grille est reliée à un potentiel haut, alors la source et le drain seront électriquement isolés. Si la grille est reliée à un potentiel de 0 volt il y aura conduction entre la source et le drain. Le transistor de type P fait bien passer le 1 (depuis la source vers le drain), mais assez mal le 0.

- La masse

- Le potentiel haut

- Traduction des potentiels hauts et de la masse

Lorsqu'un point du circuit est à un potentiel de 0 volt, on dira qu'il vaut la valeur binaire 0.

Lorsqu'un point du circuit est à un potentiel de 2 volts, on dira qu'il vaut la valeur binaire 1.

Remarque : La technologie MOS peut utiliser des potentiels hauts très variables. Nous choisirons ici une technologie de 2 volts.

Le transistor NMOS (type N) est un circuit électronique ayant 3 points importants : la source notée S, le drain noté D et la grille notée G. Le comportement de ce circuit est le suivant : si la grille est reliée à un potentiel de 0 volt, alors la source et le drain seront électriquement isolés, on dit que le transistor est bloqué. Si la grille est reliée à un potentiel haut (2 volts) par exemple) il y aura conduction entre la source et le drain, on dit que le transistor est passant. Schématiquement il s'agit donc d'un interrupteur commandé par un signal électrique. Une contrainte supplémentaire propre à la technologie MOS est que le transistor de type N fait bien passer le 0 (depuis la source vers le drain), mais assez mal le 1.

Le transistor PMOS (type P) est un circuit électronique ayant 3 points importants : la source notée S, le drain noté D et la grille notée G. Le comportement de ce circuit est le suivant : si la grille est reliée à un potentiel haut, alors la source et le drain seront électriquement isolés. Si la grille est reliée à un potentiel de 0 volt il y aura conduction entre la source et le drain. Le transistor de type P fait bien passer le 1 (depuis la source vers le drain), mais assez mal le 0.

Lorsqu'un point du circuit est à un potentiel de 2 volts, on dira qu'il vaut la valeur binaire 1.

Synthèse de portes logiques

A partir des transistor N et P, de la masse et du potentiel haut, on peut réaliser des portes logiques. Toutes les portes logiques sont réalisables quelle que soit leur table de vérité. En pratique, la plupart des portes logiques ont un nombre d'entrées et de sorties raisonnables (moins de 5 en général). Nous allons étudier quelques portes logiques usuelles.

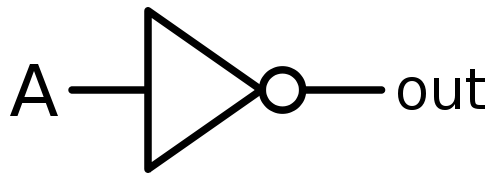

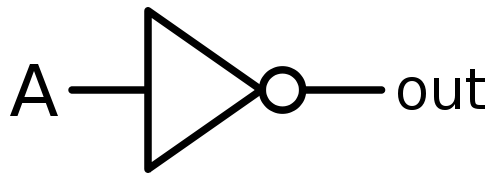

L'inverseur

Schéma :

Notation :

Un inverseur est un circuit avec une entrée A et une sortie B. Il est constitué deux 2 transistors comme sur le schéma.

- Lorsque A sera à un potentiel de 0 volt, la grille du transistor P du haut sera reliée à un potentiel de 0 volt. Il y aura donc conduction entre la source et le drain de ce transistor. le point B sera donc relié au potentiel haut. Le transistor N du bas aura lui sa grille au potentiel 0 volt. Il n'y aura donc pas conduction entre la masse (source) et le point B (drain). B sera donc au potentiel haut.

- Lorsque A sera à un potentiel haut, la grille du transistor P du haut sera reliée à un potentiel de 2 volts. La source et le drain de ce transistor seront donc électriquement isolés. Il n'y aura donc pas de conduction entre le point B et le potentiel haut. Le transistor N du bas aura lui sa grille au potentiel haut. Il y aura donc conduction entre la masse et le point B. B sera donc au potentiel de 0 volt.

- Table de vérité

La table de vérité donne la valeur des sorties pour toutes les valeurs possibles des entrées.

Table de vérité :

Notation :

Un inverseur est un circuit avec une entrée A et une sortie B. Il est constitué deux 2 transistors comme sur le schéma.

Table de vérité :

| A | B |

|---|---|

| 0 | 1 |

| 1 | 0 |

La porte NAND ou NON-ET

La sortie est l'inverse de celle d'une porte ET, donc elle n'est à zéro que si les deux entrées sont à 1.

Table de vérité :

| A | B | S |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

La porte AND ou ET

| A | B | S |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

La sortie est à 1 uniquement si A ET B sont à 1.

La porte NOR ou NON-OU

Inverse de la porte OU : la sortie n'est à 1 que si les deux entrées sont à 0.

| A | B | S |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

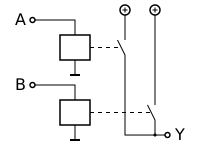

La porte OR ou OU

Pour obtenir une porte OU (ou OR) on ajoute un inverseur à la sortie de la porte NOR. Ainsi la sortie est à 1 si A ou B est à 1 (ou les deux, on parle de OU inclusif)

Schéma :

Fichier:Or.gif ou

Notation :

Schéma :

Fichier:Or.gif ou

Notation :

| A | B | S |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

La porte XOR

C'est le OU exclusif : la sortie est à 1 si une seule des deux entrées est à 1.

| A | B | S |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

La porte XNOR

C'est le OU exclusif inversé.

| A | B | S |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

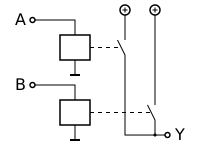

Le multiplexeur (MUX 1 bit)

Si C vaut 1, la sortie vaut A, sinon la sortie vaut B.

| C | A | B | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

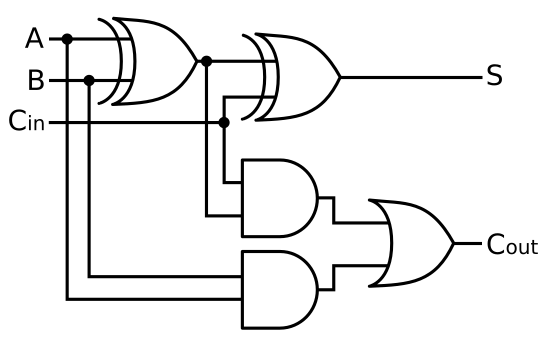

Additionneur 1 bit

| Cin | A | B | Cout | S |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

On a la relation A+B+C=2R+S, R (Cout) est donc la retenue sortante. On peut dessiner un circuit un peu plus complexe à partir des portes vues plus haut :

- R vaut 1 dès que deux entrées sont à 1 : (A AND B) OR (A AND C) OR (B AND C)

- S vaut 1 si un nombre impair d'entrées est à 1 : (A XOR B) XOR C

Assemblage de portes logiques de base

Une fois les différentes portes logiques synthétisées par des assemblages de transistors, il suffit d'assembler ces différentes portes logiques pour réaliser des circuits beaucoup plus complexes réalisant par exemple des opérations arithmétiques.

Additionneur base 2 sur 8 bits[modifier]

Soit A et B deux entiers positifs en base 2 notés respectivement (A7 A6 A5 A4 A3 A2 A1 A0) et (B7 B6 B5 B4 B3 B2 B1 B0). On veut calculer la somme S=A+B.

S est sur 8 bits et est noté (S7 S6 S5 S4 S3 S2 S1 S0). Le bit C indique la validité du résultat : C=0 indique que le résultat est valide. C=1 indique que A+B n'est pas représentable en base 2 sur 8 bits car A+B>255.

Ce circuit comporte donc 16 bits en entrée en 9 bits en sortie.

L'intérêt de la représentation des entiers relatifs en complément à 2 est que le circuit est exactement le même pour leur addition, sans se soucier de leur signe. La seule différence est que C indique que le résultat calculé est négatif, et qu'il est un peu plus complexe de vérifier que le résultat est correct (qu'il n'y a pas eu de débordement).

Soit A et B deux entiers positifs en base 2 notés respectivement (A7 A6 A5 A4 A3 A2 A1 A0) et (B7 B6 B5 B4 B3 B2 B1 B0). On veut calculer la somme S=A+B.

S est sur 8 bits et est noté (S7 S6 S5 S4 S3 S2 S1 S0). Le bit C indique la validité du résultat : C=0 indique que le résultat est valide. C=1 indique que A+B n'est pas représentable en base 2 sur 8 bits car A+B>255.

Ce circuit comporte donc 16 bits en entrée en 9 bits en sortie.

L'intérêt de la représentation des entiers relatifs en complément à 2 est que le circuit est exactement le même pour leur addition, sans se soucier de leur signe. La seule différence est que C indique que le résultat calculé est négatif, et qu'il est un peu plus complexe de vérifier que le résultat est correct (qu'il n'y a pas eu de débordement).

Additionneur/soustracteur base 2 sur 4 bits

Fichier:Additionneur-soustracteur-4 bits.gif

Soit A et B deux entiers positifs en base 2 notés respectivement (A3 A2 A1 A0) et (B3 B2 B1 B0).

Le résultat S est sur 4 bits et est noté (S3 S2 S1 S0).

Si T=0 alors S=A+B et si T=1 alors S=A-B.

Le bit C indique la validité du résultat : C=0 indique que le résultat est valide. C=1 indique que le resultat n'est pas représentable.

Ce circuit comporte donc 9 bits en entrée et 5 bits en sortie.

Soit A et B deux entiers positifs en base 2 notés respectivement (A3 A2 A1 A0) et (B3 B2 B1 B0).

Le résultat S est sur 4 bits et est noté (S3 S2 S1 S0).

Si T=0 alors S=A+B et si T=1 alors S=A-B.

Le bit C indique la validité du résultat : C=0 indique que le résultat est valide. C=1 indique que le resultat n'est pas représentable.

Ce circuit comporte donc 9 bits en entrée et 5 bits en sortie.

Multiplexeur à 2 entrées sur 8 bits

Soit A et B deux données sur 8 bits notées respectivement (A7 A6 A5 A4 A3 A2 A1 A0) et (B7 B6 B5 B4 B3 B2 B1 B0). Le bit en entrée C indique qu'on veut récupérer sur la sortie soit A soit B.

Le résultat S est sur 8 bits et est noté (S7 S6 S5 S4 S3 S2 S1 S0).

Si C=0 alors S=A et si C=1 alors S=B.

Ce circuit comporte donc 17 bits en entrée et 8 bits en sortie.

Soit A et B deux données sur 8 bits notées respectivement (A7 A6 A5 A4 A3 A2 A1 A0) et (B7 B6 B5 B4 B3 B2 B1 B0). Le bit en entrée C indique qu'on veut récupérer sur la sortie soit A soit B.

Le résultat S est sur 8 bits et est noté (S7 S6 S5 S4 S3 S2 S1 S0).

Si C=0 alors S=A et si C=1 alors S=B.

Ce circuit comporte donc 17 bits en entrée et 8 bits en sortie.

Multiplexeur à 4 entrées sur 8 bits

On peut le construire avec 3 multiplexeurs 2 entrées. Si les entrées sont A, B, C, D, le premier multiplexeur sélectionne soit A soit B, le deuxième soit C soit D, le troisième soit la sortie du premier, soit celle du deuxième.

Décaleur de 0 ou 1 bit sur 8 bits

Soit A une données sur 8 bits notée (A7 A6 A5 A4 A3 A2 A1 A0) et C une entrée sur un bit. Le bit en entrée C indique s'il faut décaler A d'un bit vers la gauche ou non..

Le résultat S est sur 8 bits et est noté (S7 S6 S5 S4 S3 S2 S1 S0).

Si C=0 alors S=A et si C=1 alors S est obtenu en décalant tous les bits de A d'un bit vers la gauche.

Ce circuit comporte donc 9 bits en entrée et 8 bits en sortie.

Soit A une données sur 8 bits notée (A7 A6 A5 A4 A3 A2 A1 A0) et C une entrée sur un bit. Le bit en entrée C indique s'il faut décaler A d'un bit vers la gauche ou non..

Le résultat S est sur 8 bits et est noté (S7 S6 S5 S4 S3 S2 S1 S0).

Si C=0 alors S=A et si C=1 alors S est obtenu en décalant tous les bits de A d'un bit vers la gauche.

Ce circuit comporte donc 9 bits en entrée et 8 bits en sortie.

Décaleur 4 bits - de 0 à 3 positions

Additionneur à 3 entrées

Multiplieur à 2 entrées sur 4 bits

Toutes les fonctions booléennes peuvent être réalisées sous forme de circuit[modifier]

Les circuits précédents (additionneur, multiplexeur, ...) sont appelés circuits combinatoires, ou circuits fonctionnels. Ils réalisent une fonction (au sens mathématique) : la sortie est complètement déterminée par les valeurs des entrées, le circuit n'a pas de « mémoire », la sortie ne dépend pas du passé. En fait on peut réaliser comme cela n'importe quelle fonction booléenne. Étant donnée une table de vérité, on peut par exemple observer pour quelles valeurs des entrées la sortie vaut 1. Un réseau de portes ET (et des inverseurs) peut vérifier que les entrées correspondent à une ligne donnée de la table de vérité. On peut construire un tel réseau pour chaque ligne dont la sortie vaut 1. Il ne reste plus qu'à assembler ces réseaux avec des portes OU. Bien sûr, ce n'est pas très économique. On peut ensuite utiliser des simplifications. Cette démarche correspond à la forme normale disjonctive de la fonction booléenne.

De façon duale, on peut utiliser la forme normale conjonctive, on peut aussi observer seulement les lignes dont la sortie est 0. Pour en savoir plus sur la conception d'un circuit à partir de sa table de vérité, voir le wikilivre Électronique numérique : logique.

- Cours et polycopiés en ligne

- Cours d'architecture des ordinateurs , Robin Fercoq,

- Cours d'architecture des ordinateurs , Carine Pivoteau,

- Cours d'architecture des ordinateurs , Frédéric Goualard,

- Cours d'architecture des ordinateurs , Emmanuel Viennet,

- Cours d'architecture des ordinateurs , Jean-Christophe Dubacq,

test to embed -

test to embed -

test to embed -

Ce plan est donné à titre indicatif. Il est pourra être modifié au fil de l'avancement réel du cours.

test to embed -

test to embed -

TD 1 - Échauffement -

- Numérations et changements de base

- Arithmétique binaire

Lien: Convertisseur binaire-décimal-hexadécimal

COURS 1 - Introduction -

- Bref historique

- Architecture en couches: plan du cours

- Couche circuits logiques

Liens: Histoire de l'informatique - Chronologie de l'informatique - Machine à différences 2

TD 2 - Codage de l'information -

- Codage des entiers

- Entiers non signés

- Entiers signés

- Complément à 2

- Codage des nombres flottants

- Codage des caractères

- Autre format numérique: images bitmap

Lien: Convertisseur IEEE 754 (applet)

TD 3 - Portes logiques et premiers circuits -

- Circuits logiques

- Fonctions booléennes

- Tables de Karnaugh

COURS 2 - Circuits logiques -

- Circuits combinatoires

- Circuits arithmétiques

TD 4 - Circuits logiques (suite) -

TD 5 - Circuits logiques non séquentiels -

- Circuits combinatoires

- Circuits arithmétiques

COURS 3 - Structure de l'ordinateur -

- Circuits séquentiels

- Mémoire

- Machine de Von Neumann

- Bus

TD 6 - Circuits séquentiels -

- Bascules

- Horloge

- Circuits à mémoire

TD de révisions -

| EXAM - |

COURS 4 - Couche micro-architecture -

- Chemin des données

- Boucle d'exécution des micro-instructions

- Micro-instructions

- Pipeline

- Cache

TD 7 - Autour de la pile - 7 novembre 2012

- Manipulation de la pile

- Calculs à l'aide d'une pile

- Instructions

TD 8 - Autour de la pile (suite) -

Feuille de TDCOURS 5 - Couches ISA (et OS) -

- Retour sur le cache

- Assembleur x86

- Registres

- Modes d'adressage

- Instructions

Liens: Jeu d'instructions x86 - x86 WikiBook - Liste réduite d'instructions x86 (IUT Arles) - Règles de choix des opérandes pour les instructions NASM

TD 9 - Couche ISA -

- Mémoire et modes d'adressage

- Masques

- Instructions de branchement

TP 1 - NASM et Insight (gdb) - .. novembre 2012

COURS 6 - Programmer en Assembleur -

Transparents de cours - (4 par page)

rayures.asm

TP 2 - Assembleur -

TP 3 - Assembleur -

Feuille de TPLien: Manuel NASM (chap. 3) - NASM en 64 bits

COURS 7 - De l'Assembleur aux langages "haut-niveau" -

- Fonctions

- Variables locales

- Tableaux

somme_rec.asm - somme.asm - tab_carres.asm - fibo.asm - majuscule.asm

TP 4 - Assembleur - ..TP 5 - Assembleur - ..

Feuille de TP | EXAM |

Document fourni: la liste des instructions en assembleur x86.

Les Livres:

LL

- Architecture et technologie des ordinateurs de Paolo Zanella, Yves Ligier, Editeur: Dunod; Édition : 4e édition, 2005, Collection : Sciences Sup.

- Architecture des ordinateurs de Jean-Jacques Schwarz, Editeur : Eyrolles, 2005.

- Architecture de l'ordinateur de Emmanuel Lazard, Editeur : Pearson Education, 2009, Collection : Synthex

- Architecture de l'ordinateur (1Cédérom) de Andrew Tanenbaum (Auteur), Editeur : Pearson Education; Édition : 5e édition, Collection : INFORMATIQUE

- Architecture des ordinateurs : Interfaces et périphériques, cours avec exercices corrigés de Philippe Darche, Collection : Passeport pour l'informatique

- Architecture de l'ordinateur : Portes logiques, circuits combinatoires, arithmétique binaire, circuits séquentiels et mémoires, exemple d'architecture de Robert Strandh, Irène Durand, Editeur : Dunod, Collection : Sciences Sup.

- Architecture de l'ordinateur, Emmanuel Lazard, Pearson Education

- Concevoir son microprocesseur, Jean-Christophe BUISSON, Ellipses

test to embed -

Les video des cours